74LS164 là thanh ghi dịch tốc độ cao với đầu vào dữ liệu nối tiếp và đầu ra dữ liệu song song. Nó là vi mạch 8-bit. Điều đó có nghĩa là dữ liệu đi vào IC từng bit một cách tuần tự và dữ liệu 8 đưa ra ở các chân đầu ra.

Dữ liệu ở đầu vào nối tiếp được đưa tới đầu vào 1 cổng logic AND và đồng bộ với sự chuyển đổi từ mức logic thấp đến cao của xung clock. Nói cách khác, sự chuyển đổi dữ liệu được xử lý khi có xung cạnh tích cực của đầu vào xung nhịp.

Nó còn được gọi với các tên như SN54164, SN54LS164, SN74164, SN74LS164

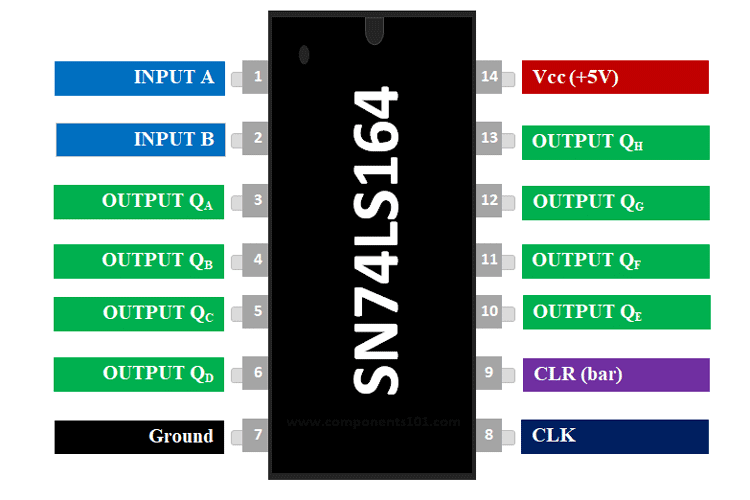

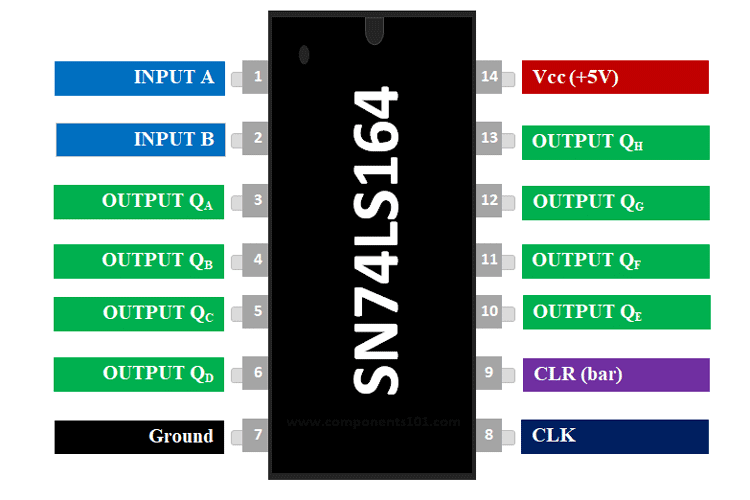

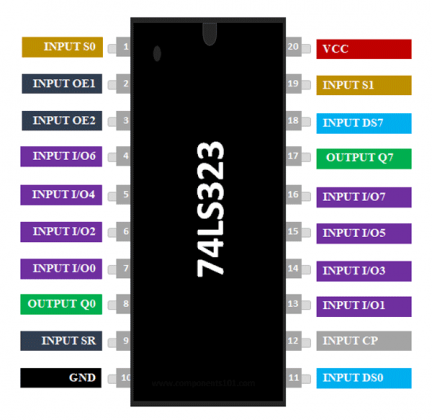

Chi tiết sơ đồ chân 74LS164

Hình dưới đây là sơ đồ chân của IC 74LS164. Như bạn có thể thấy, nó là một IC 14 chân và nó có các định dạng package khác nhau.

Chi tiết cấu hình chân 74LS164

Mô tả chi tiết của các chân IC thanh ghi dịch 74LS164:

A, B: Các chân này dùng để đưa dữ liệu nối tiếp vào IC cần chuyển ra đầu ra dữ liệu song song. Nói cách khác, đây là các chân đầu vào dữ liệu nối tiếp.

CP: Chân đầu vào này dành cho tín hiệu xung clock. Nó là chân cạnh tích cực mức cao.

~ MR: Chân này dùng để thực hiện chức năng của Master Reset. Đây là một chân đầu vào tích cực mức thấp. Tín hiệu tại chân này độc lập với xung clock, đặt tất cả các đầu ra ở mức logic thấp và xóa thanh ghi.

Q0 - Q7: Là các chân đầu ra và được sử dụng để cấp đầu ra dữ liệu song song 8 bit.

VCC = Chân cấp nguồn.

GND = Chân nối đất.

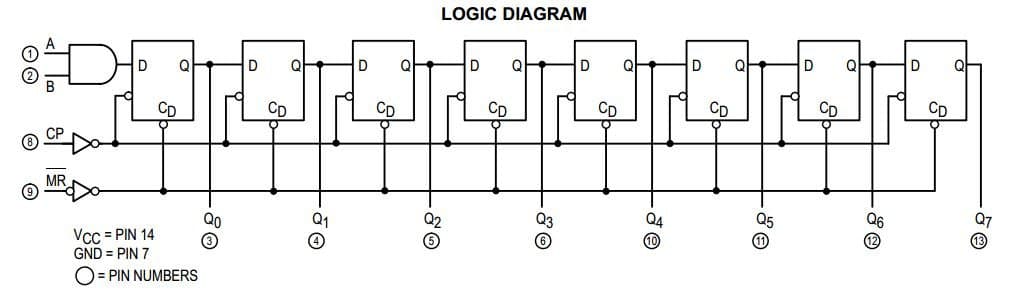

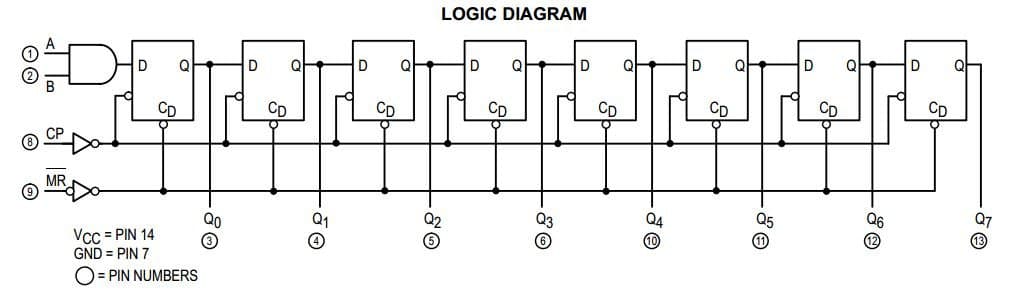

Sơ đồ logic bên trong 74LS164

Sơ đồ logic của IC thanh ghi dịch 74LS164 được thể hiện ở hình bên dưới. Bên trong nó gồm 8 flip flops , một cổng AND và hai cổng NOT.

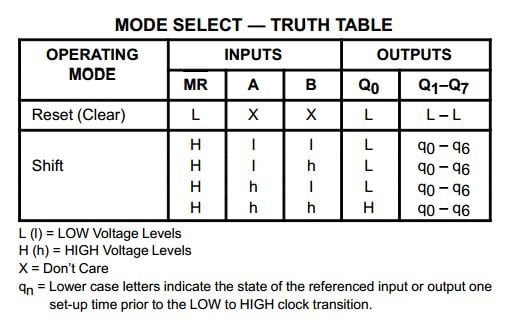

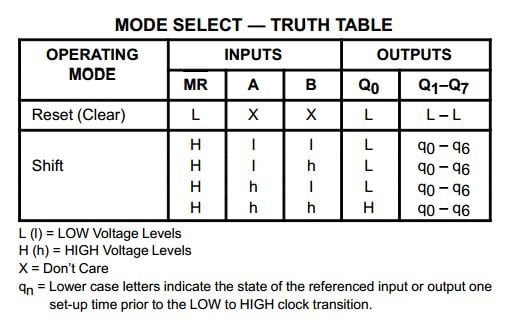

Bảng trạng thái

Bảng trạng thái về nguyên lý hoạt động của IC được thể hiện trong hình bên dưới.

IC tương tự: 74LS165, 74LS166, 74LS170, 74LS295

Nguyên lý làm việc 74LS164

~ MR là chân master reset đầu vào tích cực mức thấp. Khi trạng thái của nó ở mức thấp, bất kể dữ liệu ở đầu vào A hay B là gì thì đầu ra sẽ luôn ở trạng thái logic thấp. Vì vậy, nó có thể được gọi là Reset hoặc chế độ Clear. Để IC hoạt động ~ MR phải được đặt ở mức logic cao.

A và B là hai chân đầu vào và dữ liệu nối tiếp có thể được cấp ở bất kỳ một trong hai chân này, trong lúc đó sử dụng một chân khác ở mức logic tích cực mức cao cho phép nhận dữ liệu ở các chân đầu vào.

Bất kỳ chân đầu vào nào không được sử dụng phải được đặt ở mức logic cao, Ngoài ra cũng có thể kết nối hai chân đầu vào với nhau.

Khi có sự thay đổi của xung nhịp từ mức logic thấp lên mức logic cao, dữ liệu sẽ được dịch chuyển sang về phía bên phải và đưa vào Q0 bằng phép logic AND của hai đầu vào dữ liệu A và B.

Chuyển đổi dữ liệu ở các chân đầu ra

Khi A = B = logic cao. Q0 sẽ ở mức logic cao và dữ liệu sẽ được dịch chuyển sang phải. Ví dụ, nếu trước khi có sự thay đổi xung nhịp, dữ liệu là Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 = ab CDEFG H. Thì sau khi chuyển đổi xung nhịp đầu ra sẽ là Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 = 1 ab CDEF G. Ở đây a và b có thể ở trạng thái 1 hoặc 0 bất kỳ.

Khi A = logic = cao và B = logic thấp. Q0 sẽ ở mức logic thấp và dữ liệu sẽ được dịch chuyển sang phải. Ví dụ, nếu trước khi chuyển đổi xung nhịp, dữ liệu là Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 = ab CDEFG H. Thì sau khi chuyển đổi xung nhịp đầu ra sẽ là Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 = 0 ab CDEF G. Ở đây a và b có thể ở trạng thái 1 hoặc 0 bất kỳ.

Khi A = logic thấp và B = logic Cao. Q0 sẽ ở mức logic thấp và dữ liệu sẽ được dịch chuyển sang phải. Ví dụ, nếu trước khi chuyển đổi xung nhịp, dữ liệu là Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 = ab CDEFG H. Thì sau khi chuyển đổi xung nhịp đầu ra sẽ là Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 = 0 ab CDEF G. Ở đây a và b có thể ở trạng thái 1 hoặc 0 bất kỳ.

Khi A = logic thấp và B = logic thấp. Q0 sẽ ở mức logic thấp và dữ liệu sẽ được dịch chuyển sang phải. Ví dụ, nếu trước khi chuyển đổi xung nhịp, dữ liệu là Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 = ab CDEFG H. Thì sau khi chuyển đổi xung nhịp đầu ra sẽ là Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 = 0 ab CDEF G. Ở đây a và b có thể ở trạng thái 1 hoặc 0 bất kỳ.

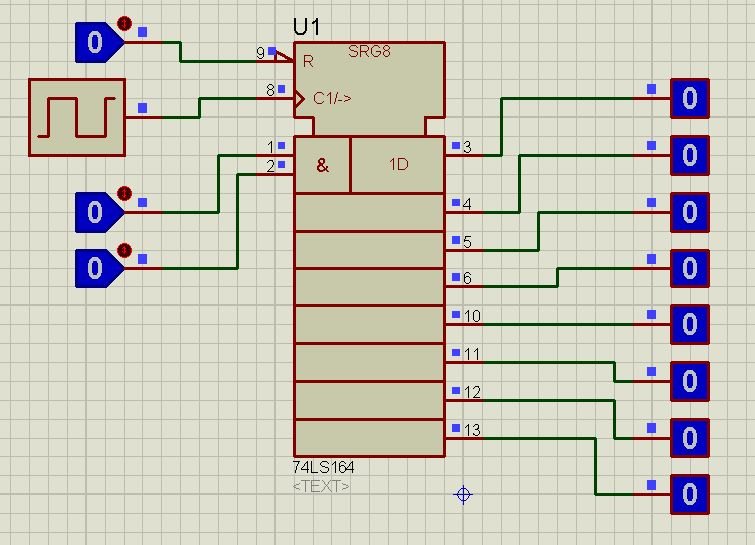

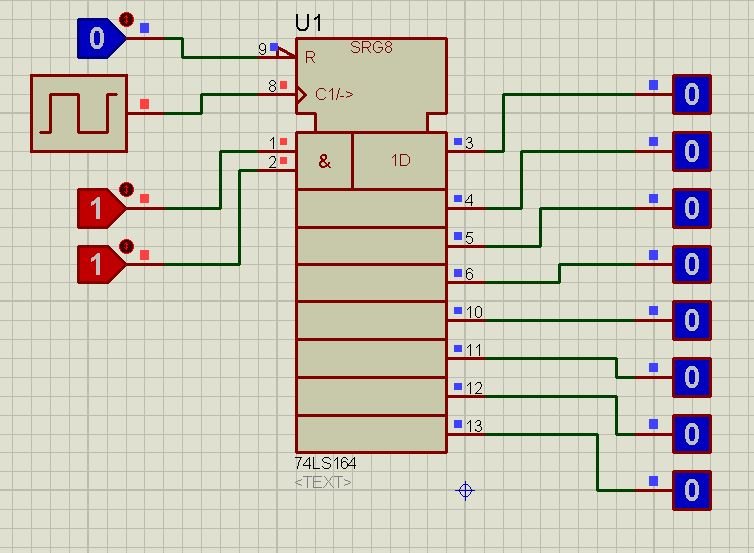

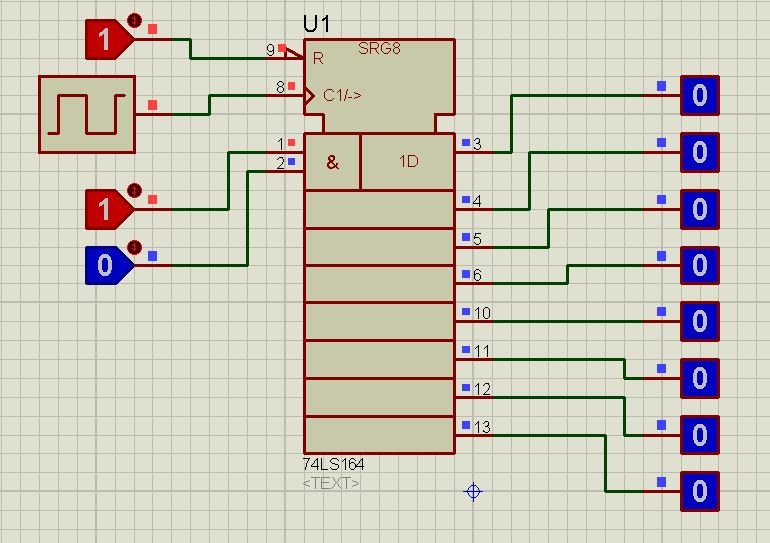

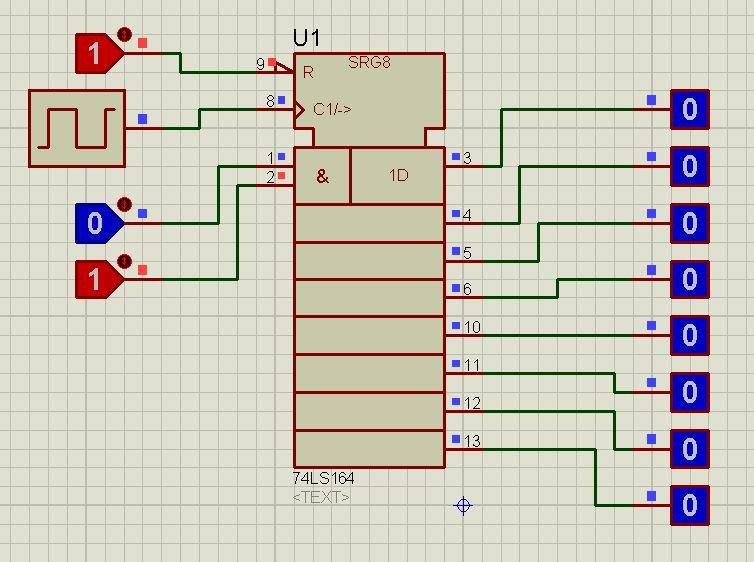

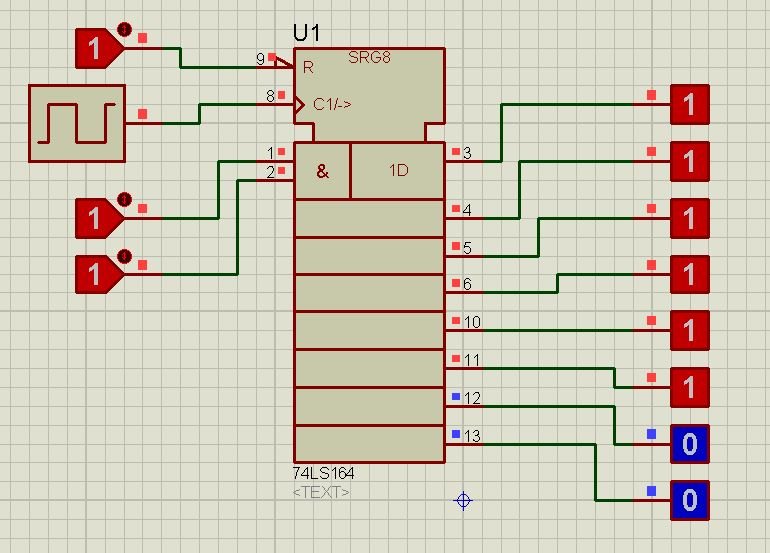

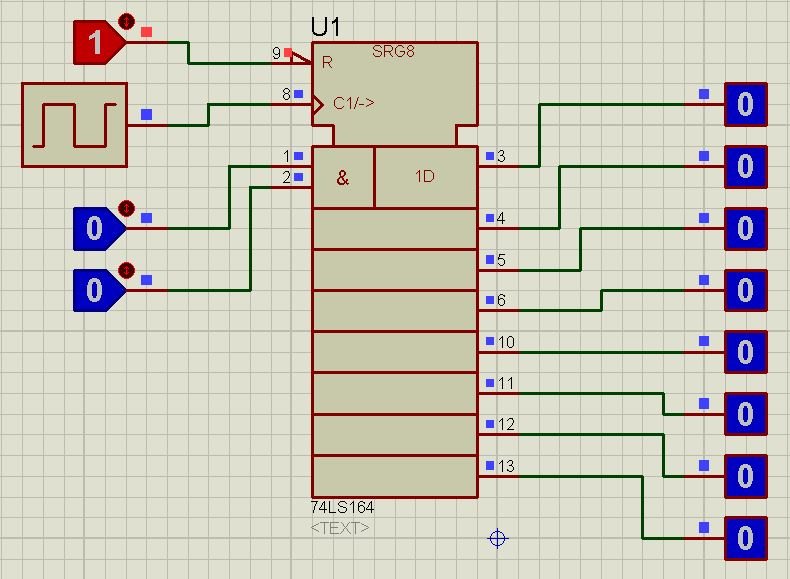

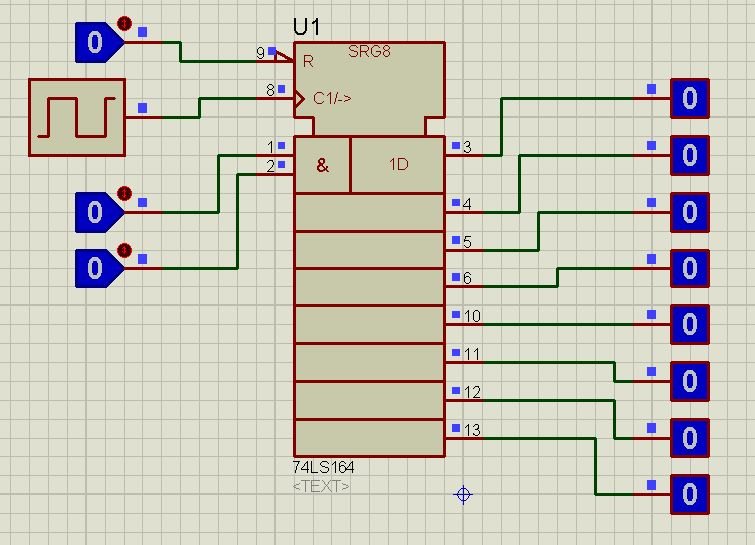

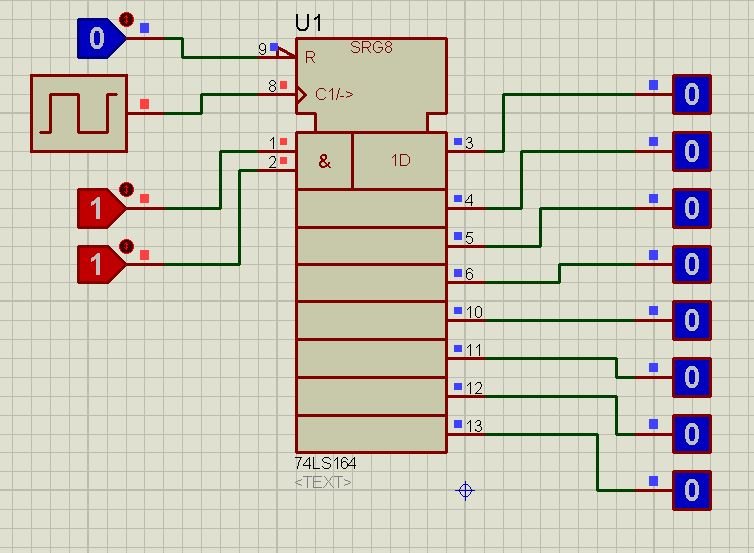

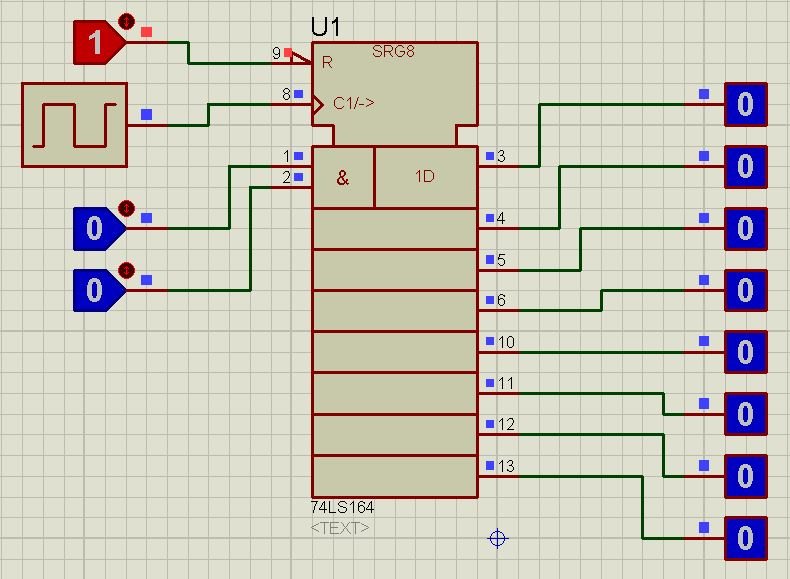

Mô phỏng Proteus 74LS164

Hoạt động của IC có thể được làm rõ qua mô phỏng trong phần mềm Proteus.

R (~ MR) hoạt động ở mức logic thấp nên khi chân 9 ở mức logic thấp, chức năng reset được thực hiện và cho dù có dữ liệu ở các chân đầu vào, nó cũng không xử lý với bất kỳ đầu vào nào.

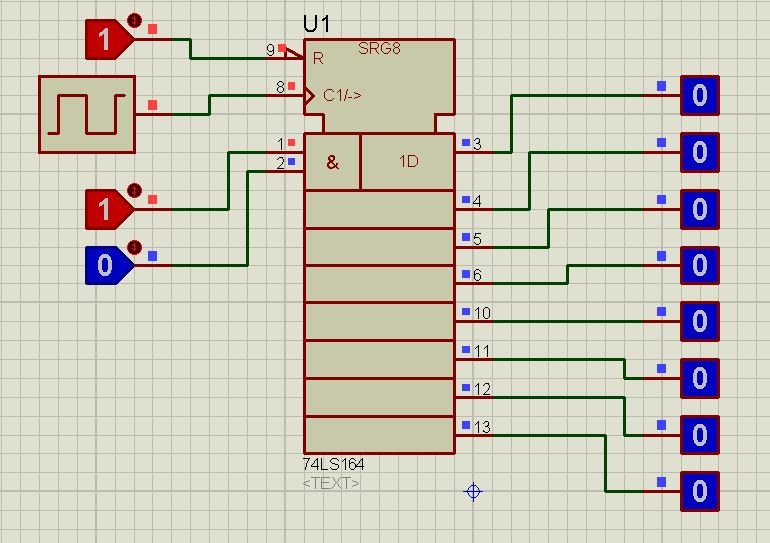

Khi A = logic cao, B = logic thấp, A & B = logic thấp, Q0 = 0 và xuất dữ liệu ở đầu ra khi kích xung nhịp.

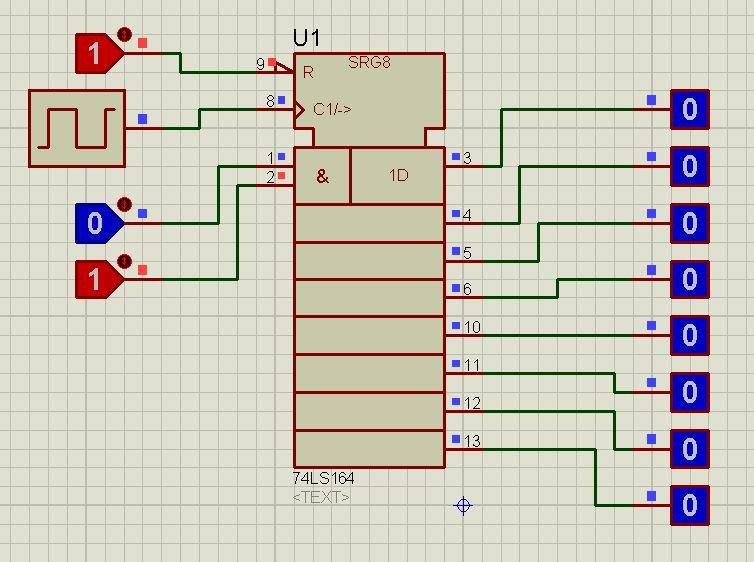

Khi A = logic thấp, B = logic cao, A & B = logic thấp, Q0 = 0 và xuất dữ liệu ở đầu ra khi kích xung nhịp.

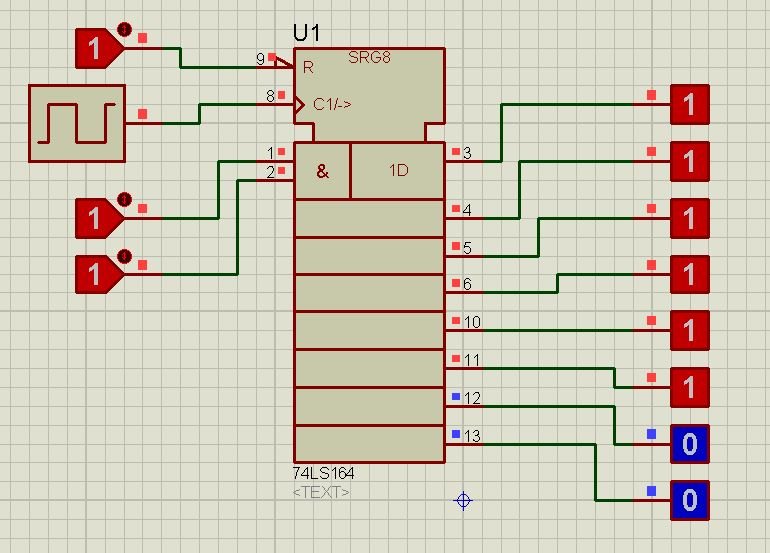

Khi A = logic cao, B = logic cao, A & B = logic cao, Q0 = 1 và xuất dữ liệu ở đầu ra khi kích xung nhịp và các bit khác dịch sang phải.

Khi A = logic thấp, B = logic thấp, A & B = logic thấp, Q0 = 0 và xuất dữ liệu ở đầu ra khi kích xung clock.

Mã đặt hàng IC thanh ghi dịch

IC này có ba biến thể như trong hình bên dưới. Định dạng đặt hàng theo những thứ này như sau.

SN54LSXXXJ

SN74LSXXXN

SN74LSXXXD

XXX = 164 và J cho biết được làm từ gốm. N cho biết có vỏ nhựa và D là package SOIC.

Đặc điểm

- Chức năng reset không đồng bộ có nghĩa là không phụ thuộc vào xung clock, nó có thể reset tất cả các chân đầu ra thành mức logic thấp.

- Truyền dữ liệu đến các chân đầu ra được đồng bộ hóa hoàn toàn (ngay lập tức).

- Hiệu ứng ngừng tốc độ cao bị hạn chế khi sử dụng diode Schottky.

- Nó có khả năng chống phóng tĩnh điện 3500 V.

- 35 MHz là tần số dịch chuyển hoạt động điển hình.

Các ứng dụng

- Bộ đếm up down digital

- Dịch dữ liệu sang trái và phải

- Chuyển đổi dữ liệu

- Ứng dụng trong ALU

- Chuyển đổi dữ liệu nối tiếp và song song

- Mạch tạo trình tự

IC thanh ghi dịch thay thế:

- Thanh ghi dịch 74HC595

- IC CD4035 thanh ghi dịch 4 giai đoạn với đầu vào dữ liệu và đầu ra dữ liệu song song

- IC CD4015 thanh ghi dịch chuyển 4 giai đoạn Serial-in / Parallel-out

- IC CD4014 thanh ghi dịch tĩnh 8 giai đoạn

- IC 74LS166 thanh ghi dịch 8-bit

- Giao tiếp 74HC595 thanh ghi dịch dữ liệu nối tiếp với vi điều khiển Pic

- Thanh ghi dịch trong labviewa

- Giao tiếp 74HC595 với màn hình led 7 đoạn và vi điều khiển Pic

>>> 100+ Mã Sản Phẩm Dây Rút: https://mecsu.vn/san-pham/quat.nKKQ

>>> 1000+ Mã Sản Phẩm Đầu Cosse: https://mecsu.vn/san-pham/dau-cosse.Q1j

>>> Mời anh em xem thêm:

Tán Lục Giác (470)

Tán Hàn - Weldnut (33)

Tán Keo - Lock Nut (226)

Tán Khía - Flange Nut (50)

Tán Dài (3)

Tán Bầu (39)

Tán Khóa (58)

Tán Cánh Chuồn (17)

Tán Cài (6)

Tán Vuông (11)

Vú Mỡ (Nipple Grease) (23)

Nut-With Knurled Heads (24)

Quick-Lock Nuts (16)

Blocks for Adjusting Bolts (207)

Threaded Stopper Blocks (52)

Bearing Lock Nuts (78)

Lông Đền Phẳng - Flat Washer (312)

Lông Đền Vênh - Spring Washer (244)

Lông Đền Vuông (25)

Lông Đền Răng (91)

Lông Đền Vênh Loại Lượn Sóng (7)

Lông Đền Lượn Sóng (15)

Lông Đền Lò Xo Đĩa (25)

Lông Đền Nord-Lock (95)

Lông Đền Heico-Lock (101)

Lông Đền Răng Cưa (77)

Lông Đền Chén (1)

Lông Đền Cầu (5)

Lông Đền Làm Kín (Dạng Phớt) (3)

Gối Đỡ Vòng Bi UCP (69)

Gối Đỡ Vòng Bi UCF (46)

Gối Đỡ Vòng Bi UCPA (6)

Gối Đỡ Vòng Bi UCFC (16)

Gối Đỡ Vòng Bi UCFL (26)

Gối Đỡ Vòng Bi UCFK (3)

Gối Đỡ Vòng Bi UCT (16)

Gối Đỡ UCHA (2)

Gối Đỡ Vòng Bi Đũa Hình Tròn (1)

Vòng Bi Chuyên Dùng Cho Gối Đỡ (1)

Vòng Bi Chuyên Dùng Cho Gối Đỡ (1)

Vòng Bi UC (45)

Vòng Bi UK (3)

Vỏ Gối Đỡ (22)

Phụ Kiện Gối Đỡ (27)

Con Lăn Bi Loại Ép Chặt (7)

Con Lăn Bi Loại Thân Lục Giác (14)

Con Lăn Bi Loại Thân Tròn (5)

Con Lăn Bi Loại Đế Mặt Bích (4)

Con Lăn Bi Loại Đinh Tán Đầu Tròn (4)

Con Lăn Bi Loại Vít Cấy (12)

Con Lăn Bi Loại Đẩy Bi Có Ren (3)

Con Lăn Bi Loại Đẩy Bi Không Ren (3)

Ball Rollers Press (1)

Ball Plungers Roller (10)

Press Fit Plungers Roller (6)

Đầu Nối Nhanh Khí Nén Thẳng (1340)

Đầu Nối Nhanh Khí Nén Thẳng - Có Ren (2935)

Đầu Nối Nhanh Khí Nén Cong (585)

Đầu Nối Nhanh Khí Nén Cong - Có Ren (2995)

Đầu Nối Nhanh Khí Nén Chữ Y (475)

Đầu Nối Nhanh Khí Nén Chữ Y - Có Ren (557)

Đầu Nối Nhanh Khí Nén Chữ T (514)

Đầu Nối Nhanh Khí Nén Chữ T - Có Ren (1790)

Đầu Nối Nhanh Khí Nén Chữ Thập (70)

Đầu Nối Nhanh Khí Nén Lắp Vách (106)

Đầu Nối Khí Nén Kim Loại (1)

![[Tìm hiểu] 74LS164 IC thanh ghi dịch](https://cms.mecsu.vn/uploads/media/2023/08/so-do-chan-74LS164-630x420.png)

![[Tìm hiểu] EL357 Optocoupler - Transistor output](https://cms.mecsu.vn/uploads/media/2023/08/so-do-chan-EL357-696x286.jpeg)

![[Tìm hiểu] Module ghi và phát âm thanh ISD1760](https://cms.mecsu.vn/uploads/media/2023/08/so-do-chan-ISD1760-425x420.jpeg)