IC CD4027 là IC flipflop JK Master / Slave. IC này gồm hai flip flops JK với các đầu ra Q và ~ Q. Mỗi flip flop JK có các chân điều khiển reset, set, clock và JK.

Thuộc dòng mạch tích hợp CD4000 được thiết kế với các transistor kênh N và P. Tất cả các đầu vào của CD4027 đều được bảo vệ chống phóng tĩnh điện bằng các diode được mắc vào giữa chân VDD và VSS. Có nhiều package 14 chân PDIP, GDIP, PDSO.

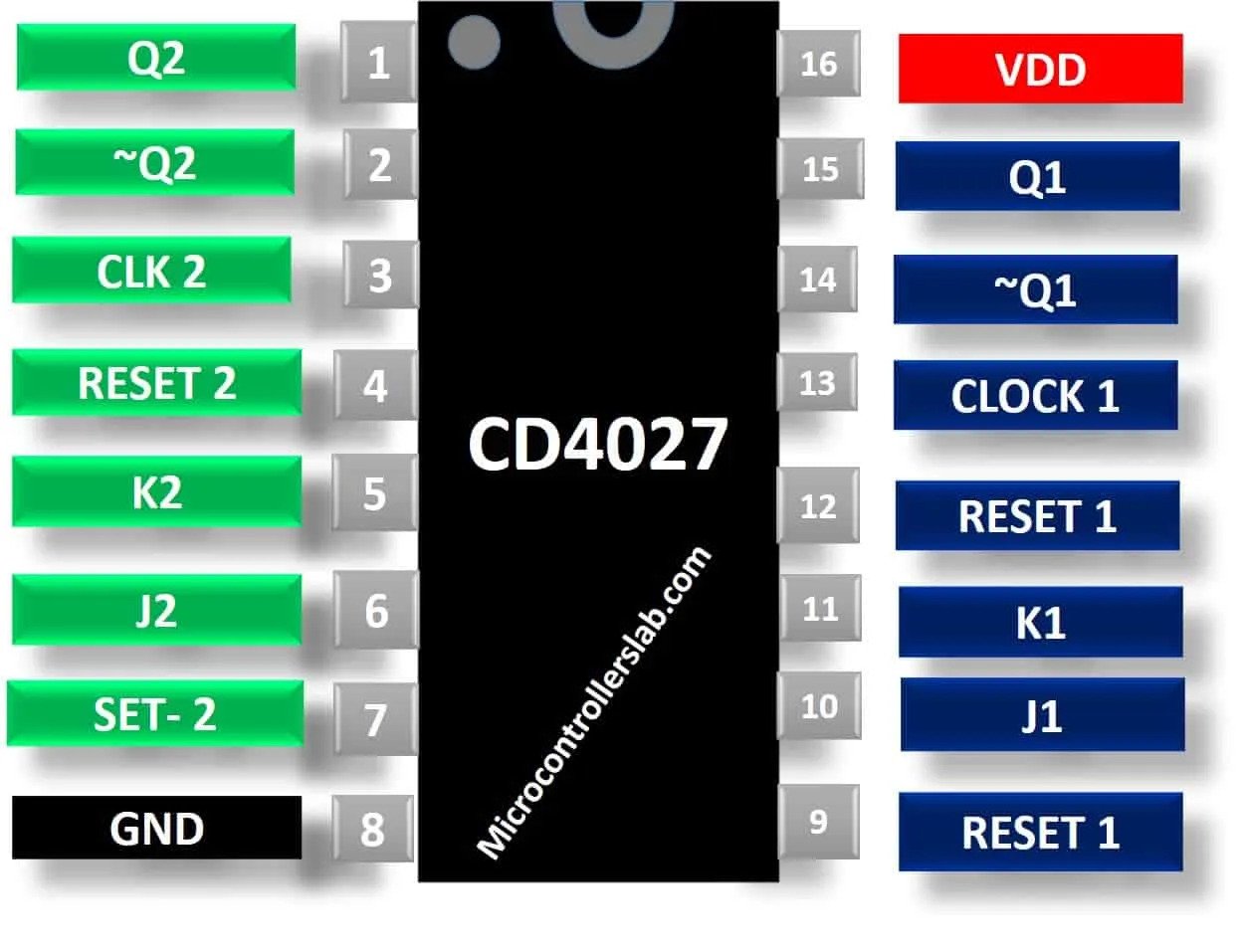

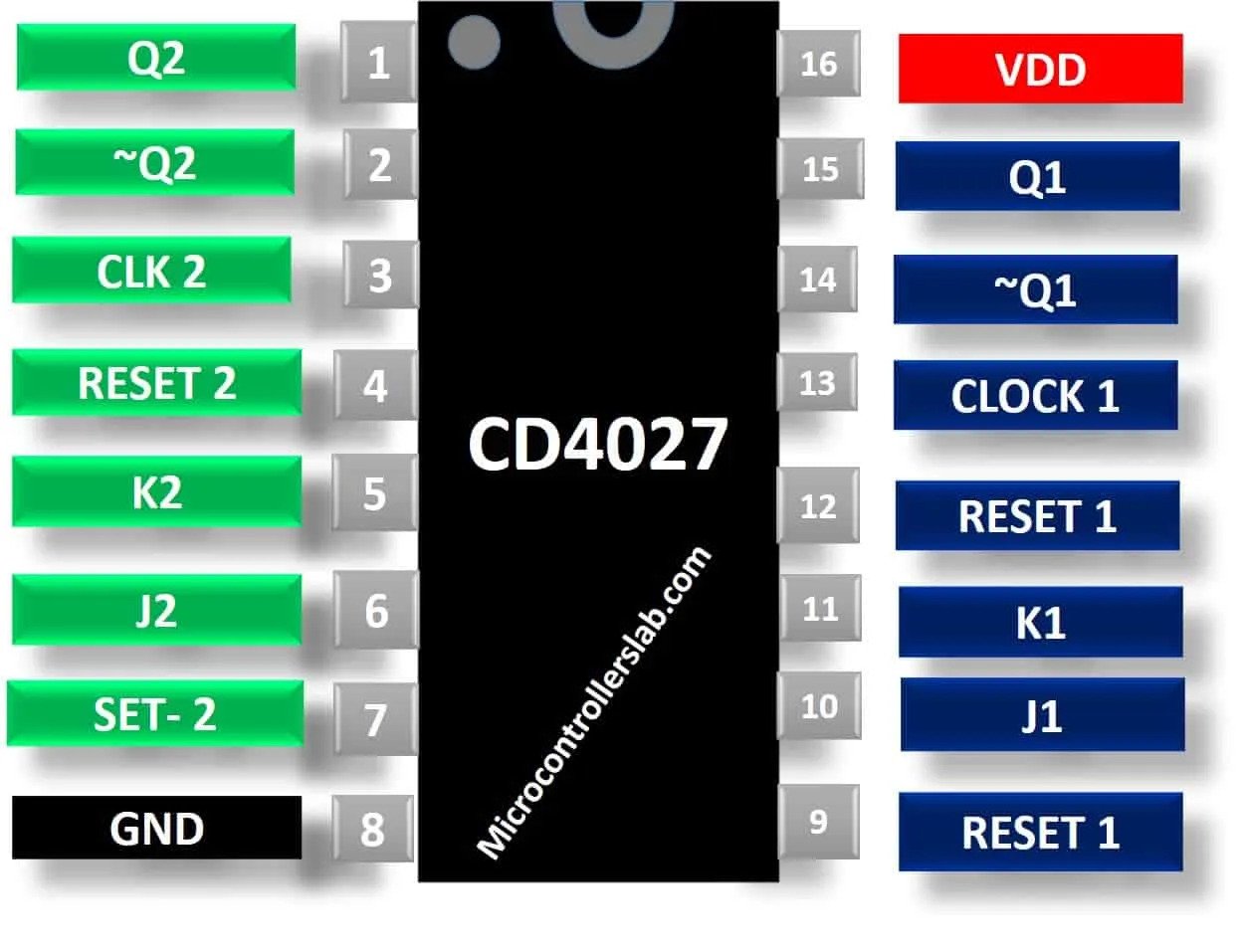

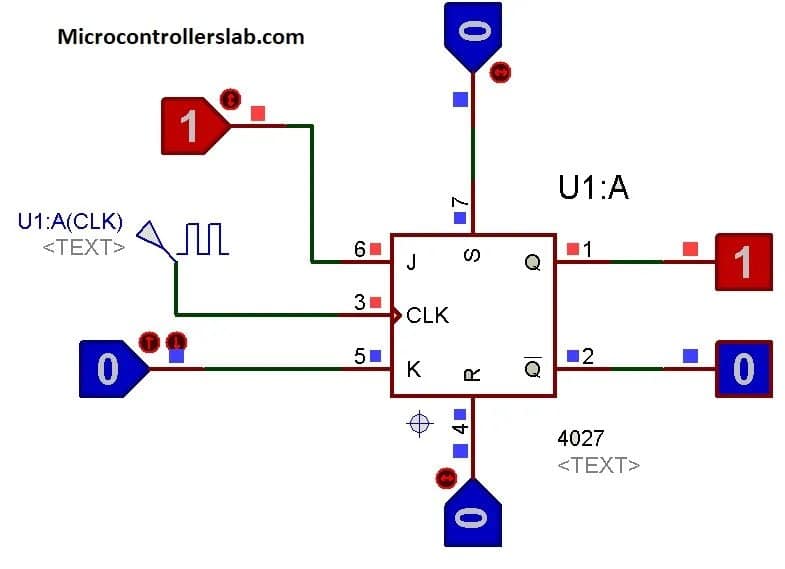

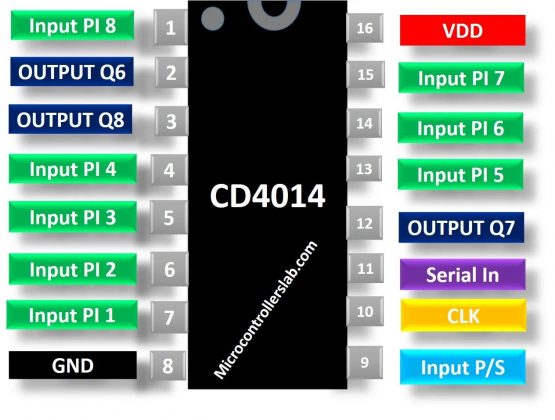

Sơ đồ CD4027

Mô tả cấu hình chân

IC CD4027 có tổng cộng 16 chân. Là IC flip flop kép nên nó có 2 flip flop. Tất cả các chân, tên và mô tả chức năng của chúng được đề cập trong bảng dưới đây.

| Số chân |

Tên chân |

Mô tả |

| 1, 15 |

Q2, Q1 |

Chân đầu ra |

| 2, 14 |

~Q2,~Q1 |

Chân đầu ra đảo |

| 3, 13 |

CLOCK 2, CLOCK 1 |

Xung clock |

| 4, 12 |

RESET 2, RESET 1 |

Khi chân này có mức logic thấp, giá trị của Q sẽ là 1.

Khi chân này có mức logic cao, giá trị của đầu ra ~Q sẽ là 1.

|

| 5, 11 |

K2, K1 |

Chân đầu vào 1 |

| 6, 10 |

J2, J1 |

Chân đầu vào 2 |

| 7, 9 |

SET 2, SET 1 |

Khi chân này ở mức logic cao, giá trị của Q sẽ là 1.

Khi chân này ở mức logic thấp, giá trị của ~Q sẽ là 1.

|

| 8 |

GND |

Cung cấp điện âm |

| 16 |

Vdd |

Cung cấp điện tích cực |

Các đặc tính CD4027

- Hoạt động với tốc độ trung bình 16 MHz với nguồn cung cấp 10V

- Dải điện áp từ 3.0V đến 15V

- Flip-Flop hoạt động tĩnh

- Khả năng chống nhiễu cao

- Có khả năng set và reset

- Tương thích chuẩn logic TTL

- Công suất tiêu thụ thấp 50 nW

- Thời gian tăng / giảm tín hiệu đầu vào ở 5V là 45us

- Điện áp đầu vào tối đa và tối thiểu là 2 V và 0,8 V

Lưu ý: Có thể tham khảo datasheet để biết thêm các tính năng và thông số kỹ thuật. Link datasheet ở cuối bài viết.

Các lựa chọn thay thế

74LS73, 74LS76, CD4013B, CD4042, CD4043, CD4095

Nơi ứng dụng

CD4027IC được sử dụng để lưu dữ liệu và thực hiện các chức năng điều khiển, thanh ghi dữ liệu và chuyển đổi dữ liệu. Trong ứng dụng bật tắt, nó được sử dụng để thay đổi tín hiệu bằng các tín hiệu đầu vào điều khiển.

Bạn cũng có thể sử dụng IC này trong các thiết bị chốt tín hiệu do đặc tính của nó là lưu dữ liệu và xuất tín hiệu đầu ra dựa vào trạng thái logic đầu ra trước đó.

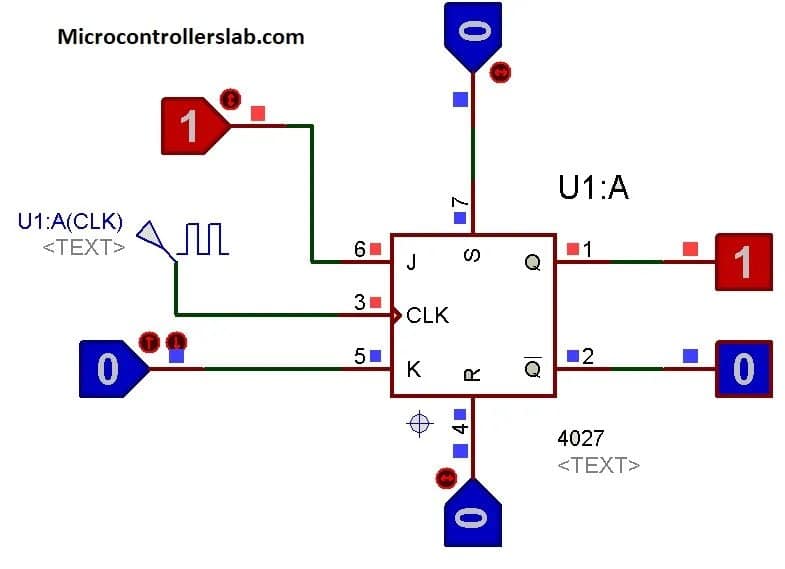

Cách sử dụng CD4027

CD4027 có hai flip flop, mỗi flip có bốn đầu vào độc lập và hai đầu ra ngược tín hiệu nhau. Các chân đầu vào J và K điều khiển trạng thái logic flip flop khi có xung cạnh tích cực cao của xung clock.

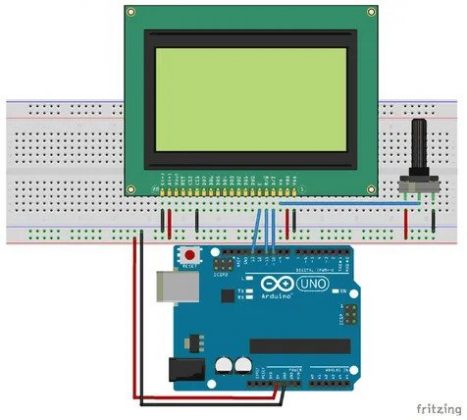

Chúng ta có thể cấp tín hiệu clock thông qua một nút nhấn hoặc tín hiệu PWM. Các chân set và reset hoạt động độc lập với xung clock. Bắt đầu hoạt động bằng cách cấp tín hiệu logic cao cho các chân này. Chân 8 được mắc với mass. Kết nối chân 16 với nguồn điện dương.

Đây là một sơ đồ mạch đơn giản cùng các tín hiệu điều khiển và xung clock. Có thể thấy, tín hiệu reset và set được đặt bằng không. Do đó, các đầu ra trên chân Q và ~ Q phụ thuộc vào tín hiệu đầu vào JK. Có thể xem bảng trạng thái sau để tìm mối hiểu rõ

Bảng trạng thái Flip Flop JK

Bảng trạng thái được hiển thị bên dưới mô tả trạng thái khi cấp các giá trị khác nhau cho đầu vào và xuất tín hiệu ra đầu ra và trạng thái logic tiếp theo của flipflop CD4027.

| Trạng thái logic hiện tại |

Trạng thái logic tiếp theo |

| CLOCK |

J |

K |

SET |

RESET |

Q |

Q |

~Q |

| Cạnh tích cực cao |

1 |

X |

0 |

0 |

0 |

1 |

0 |

| Cạnh tích cực cao |

X |

0 |

0 |

0 |

1 |

1 |

0 |

| Cạnh tích cực cao |

0 |

X |

0 |

0 |

0 |

0 |

1 |

| Cạnh tích cực cao |

X |

1 |

0 |

0 |

1 |

0 |

1 |

| Cạnh tích cực thấp |

X |

X |

0 |

0 |

X |

Không thay đổi |

Không thay đổi |

| X |

X |

X |

1 |

0 |

X |

1 |

0 |

| X |

X |

X |

0 |

1 |

X |

0 |

1 |

| X |

X |

X |

1 |

1 |

X |

1 |

1 |

Bây giờ chúng ta hãy thiết kế một ví dụ thực tế với IC flip flop JK CD4027.

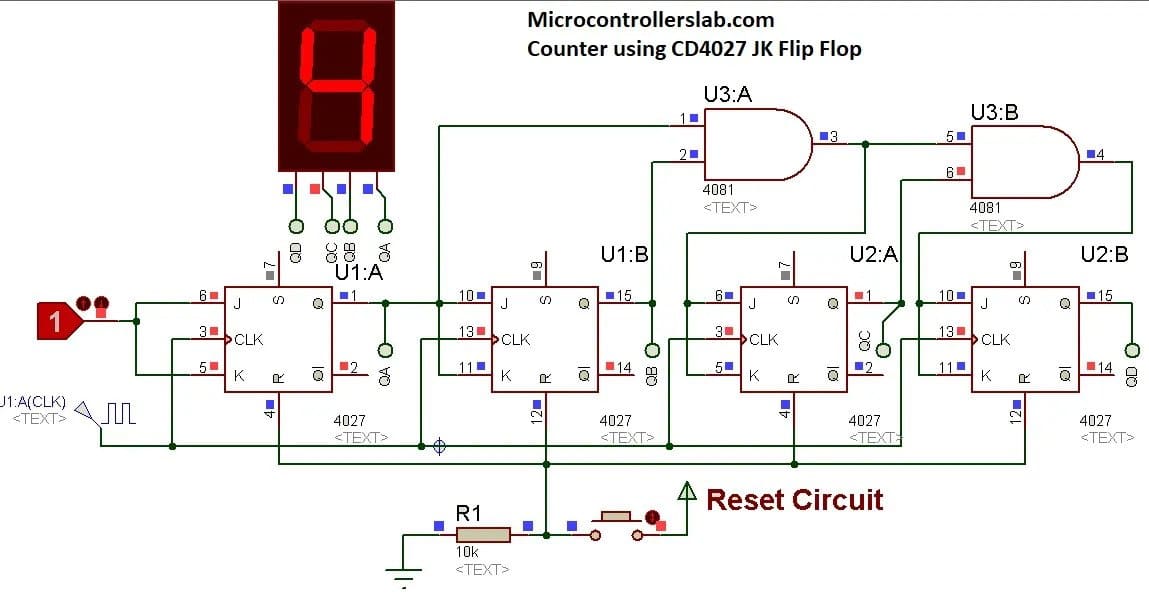

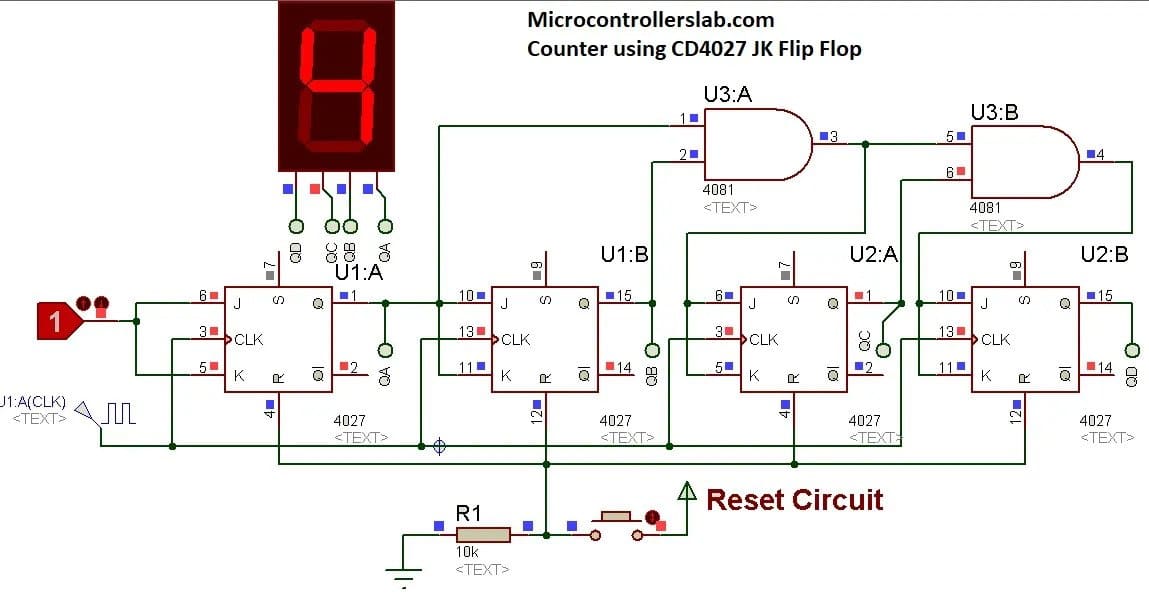

Bộ đếm nhị phân 4 bit sử dụng CD4027 JK Flip Flop

Trong ví dụ này, chúng ta sẽ thiết kế một bộ đếm nhị phân đồng bộ sử dụng bốn FlipFlop. Bộ đếm đồng bộ không có độ trễ lan truyền.

Vì kết nối tín hiệu xung nhịp với chân clock của các FF, nên tất cả các JK FF thay đổi trạng thái ngay lập tức trên mọi xung cạnh tích cực cao.

Ví dụ bộ đếm 4 bit này có 4 flipflop JK, hai cổng logic AND CD4081 và một led 7 đoạn. Mặc dù, đây là bộ đếm 4 bit và có thể hiển thị số thập phân từ 0-16. Nhưng chỉ sử dụng một led bảy đoạn.

Mô phỏng bộ đếm trên Proteus

Như bạn có thể thấy từ mô phỏng proteus, chúng ta đưa ra một tín hiệu xung clock chung cho tất cả các flipflop. Nói cách khác, tất cả các FF đều thực hiện chuyển đổi logic với cùng một tín hiệu xung clock. Kết nối các chân JK với nhau để truyền tín hiệu logic cao từ các flipflop khi có xung cạnh tích cực cao xung nhịp.

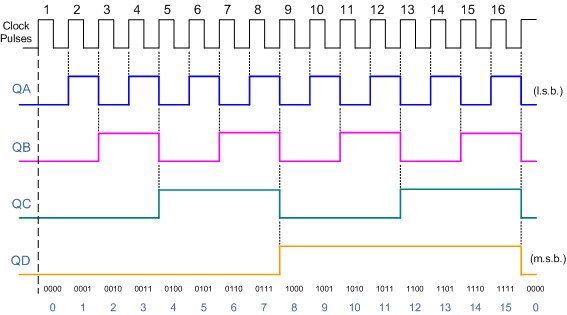

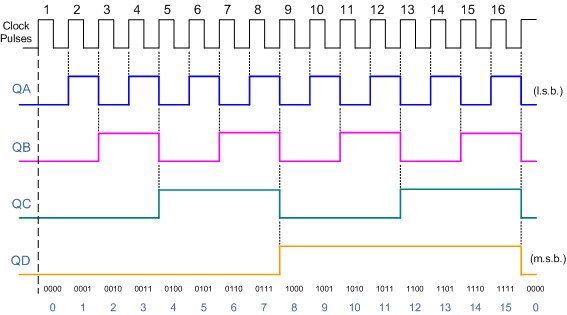

Mỗi Flipflop thay đổi trạng thái logic theo biểu đồ thời gian dưới đây.

Ứng dụng CD4027

- Mạch bộ nhớ máy tính

- Thanh ghi dịch có thể được thiết bằng vi mạch này vì chúng là các mạch logic tuần tự và chủ yếu được sử dụng để lưu dữ liệu digital

- Được sử dụng trong thanh ghi thoại (voice register) và thanh ghi bộ nhớ hoặc thanh ghi điều khiển

- Các mạch EEPROM để chứa một lượng nhỏ dữ liệu

- Các linh kiện và bộ đếm chốt dữ liệu

>>> 100+ Mã Sản Phẩm Dây Rút: https://mecsu.vn/san-pham/day-rut-nhua.5op

>>> 1000+ Mã Sản Phẩm Đầu Cosse: https://mecsu.vn/san-pham/dau-cosse.Q1j

>>> Mời anh em xem thêm

Gối Đỡ Vòng Bi Cầu UCP (74)

Gối Đỡ Vòng Bi Cầu Mặt Bích Vuông UCF (65)

Gối Đỡ Vòng Bi Cầu UCPA (9)

Gối Đỡ Vòng Bi Cầu Mặt Bích Tròn UCFC (15)

Gối Đỡ Vòng Bi Cầu Mặt Bích Hình Thoi UCFL (20)

Gối Đỡ Vòng Bi Cầu Chữ T UCT (20)

Gối Đỡ Vòng Bi Đũa UCP (3)

Gối Đỡ Vòng Bi Đũa Mặt Bích Vuông UCF (1)

Gối Đỡ Vòng Bi Mắt Trâu (20)

Gối Đỡ Hai Nửa (31)

Măng Xông Vòng Bi (3)

Vòng Bi UC - UK (82)

Vỏ Gối Đỡ (1)

Vòng Đệm Khóa (22)

Phụ Kiện Gối Đỡ (54)

Con Lăn Bi Loại Ép Chặt (7)

Con Lăn Bi Loại Thân Lục Giác (8)

Con Lăn Bi Loại Thân Tròn (5)

Con Lăn Bi Loại Đế Mặt Bích (3)

Con Lăn Bi Loại Đinh Tán Đầu Tròn (4)

Con Lăn Bi Loại Vít Cấy (4)

Con Lăn Bi Loại Đẩy Bi Không Ren (3)

Ball Rollers Press (1)

Ball Plungers Roller (10)

Press Fit Plungers Roller (6)

Bộ Đầu Cos - Terminal Kits (3)

Đầu Cosse Chĩa Chữ Y (38)

Đầu Cosse Tròn (132)

Đầu Cosse Bít SC - TL (75)

Đầu Cosse Ghim (54)

Đầu Cosse Pin Đặc (19)

Đầu Cosse Pin Dẹp (22)

Đầu Cosse Pin Rỗng (77)

Đầu Cosse Nối Thẳng (31)

Đầu Cosse Chụp Nối Dây (8)

Đầu Cosse Vuông (8)

Mũ Chụp Đầu Cosse (127)

Giắc Cắm Điện Ô Tô (14)

Others of Vòng Bi

Others of Vòng Bi

![[ Review] Các loại cờ lê Sata tốt nhất thị trường](https://cms.mecsu.vn/uploads/media/2024/09/ảnh bìa mecsu-1.jpg)