CD4068 là vi mạch theo chuẩn logic NAND / AND 8 đầu vào thuộc dòng mạch tích hợp CD4000. Đầu tiên, có hai tùy chọn đầu ra cổng AND và cổng NAND.

Tiếp theo, các chân đầu vào là giống nhau cho cả hai cổng logic. Có các package 14 chân PDIP, GDIP, PDSO. Điện áp hoạt động của IC là + 5V, nhưng cũng có thể hoạt động với điện áp + 10V và + 15V.

IC này rất hữu ích cho các ứng dụng yêu cầu mức tiêu thụ năng lượng thấp. Hơn nữa, nó có dải điện áp hoạt động rộng.

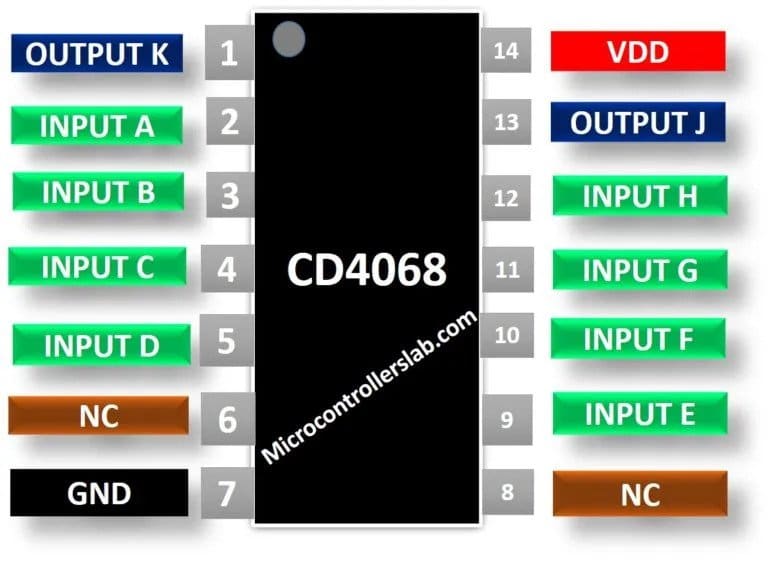

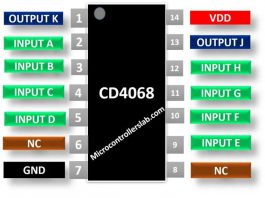

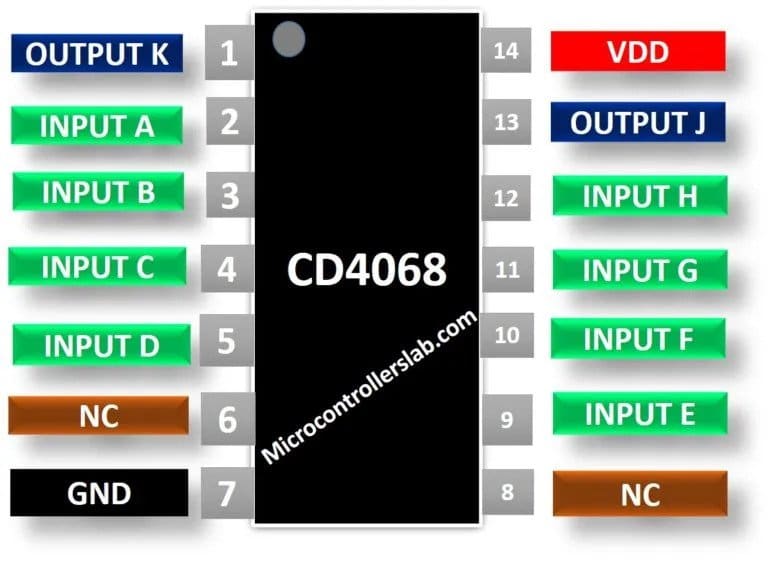

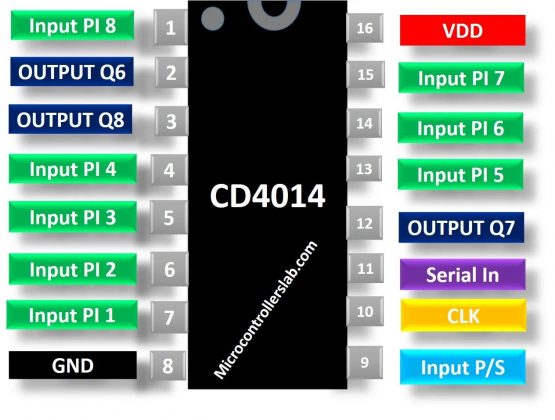

Sơ đồ chân CD4068

Đây là sơ đồ chân 14 chân của CD4068. Các chân đầu ra J và K lần lượt là của cổng logic NAND và AND.

Chi tiết cấu hình chân

| Số chân |

Tên chân |

Mô tả |

| 2, 3, 4, 5, 9, 10, 11, 12 |

A, B, C, D, E, F, G, H |

Các chân dữ liệu đầu vào |

| 1 |

K |

Đầu ra của cổng AND |

| 13 |

J |

Đầu ra của cổng NAND |

| 6, 8 |

NC |

Không có kết nối |

| 7 |

Vss |

Chân cấp nguồn âm |

| 14 |

VDD |

Chân cấp nguồn dương |

Các đặc tính của CD4068

- Cổng logic NAND / AND 8 đầu vào với các đầu vào và đầu ra được đệm tín hiệu

- Hoạt động ở tốc độ trung bình với độ trễ lan truyền 75ns khi VDD = 10V

- Điện áp hoạt động từ 3V đến 18V

- Dải dòng điện đầu ra từ -1.5mA đến 1.5mA

- Dòng điện đầu vào trên dải nhiệt độ cho phép ở 18V là 1µA trong khi đó với cùng mức điện áp nhưng ở nhiệt độ 25 ° C thì là 100nA

- Dải nhiệt độ hoạt động từ -55 đến 125 ° C

- Là loại điện áp cao (Mức 20V)

IC logic AND / NAND thay thế:

74LS00, CD4011, 74LS08

Nơi ứng dụng

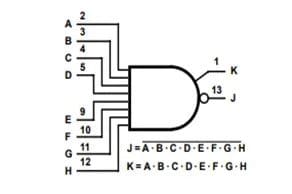

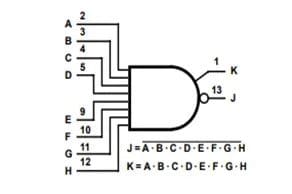

CD4068 có thể được sử dụng cho các ứng dụng yêu cầu cả cổng NAND và AND cùng với dải điện áp hoạt động rộng. IC này có 8 đầu vào và 2 đầu vào. Đầu ra J cho cổng NAND và có thể được xác định bằng phương trình logic sau:

J=(A.B.C.D.E.F.G.H)

Đầu ra K cho cổng AND. Giá trị có thể được tính toán bằng phương trình logic sau:

K=~(A.B.C.D.E.F.G.H)

Cổng AND chỉ cho giá trị logic cao khi tất cả các đầu vào của nó có mức logic cao, trong khi đó cổng NAND hoạt động theo cách ngược lại. Nó cho giá trị logic thấp khi tất cả các đầu vào của nó có mức logic 1.

Bảng trạng thái dưới đây sẽ làm rõ. Trong đó 1 là giá trị logic cao, 0 là giá trị logic thấp và X là có thể là mức logic cao hoặc thấp.

Bảng trạng thái

| ĐẦU VÀO DỮ LIỆU |

ĐẦU RA DỮ LIỆU |

| A |

B |

C |

D |

E |

F |

G |

H |

J |

K |

| 0 |

X |

X |

X |

X |

X |

X |

X |

1 |

0 |

| X |

0 |

X |

X |

X |

X |

X |

X |

1 |

0 |

| X |

X |

0 |

X |

X |

X |

X |

X |

1 |

0 |

| X |

X |

X |

0 |

X |

X |

X |

X |

1 |

0 |

| X |

X |

X |

X |

0 |

X |

X |

X |

1 |

0 |

| X |

X |

X |

X |

X |

0 |

X |

X |

1 |

0 |

| X |

X |

X |

X |

X |

X |

0 |

X |

1 |

0 |

| X |

X |

X |

X |

X |

X |

X |

0 |

1 |

0 |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

Mạch ví dụ CD4068

Để sử dụng IC CD4068, hãy cấp nguồn cho IC bằng cách kết nối cực dương của nguồn điện vào chân Vdd và cực âm hoặc nối đất vào chân Vcc.

Sau đó, cấp các tín hiệu đầu vào digital vào các chân đầu vào và sẽ nhận được tín hiệu đầu ra theo tín hiệu các đầu vào. Mức điện áp đầu ra phụ thuộc vào nguồn điện. Xem mô phỏng proteus này:

Ứng dụng CD4068

- Mạch đệm logic

- Mạch logic kết hợp

- Thiết kế bộ mã hóa và bộ giải mã

- Thiết kế bộ ghép kênh và bộ phân kênh

- Thiết kế mạch tạo dao động, mạng tín hiệu và hệ thống digital

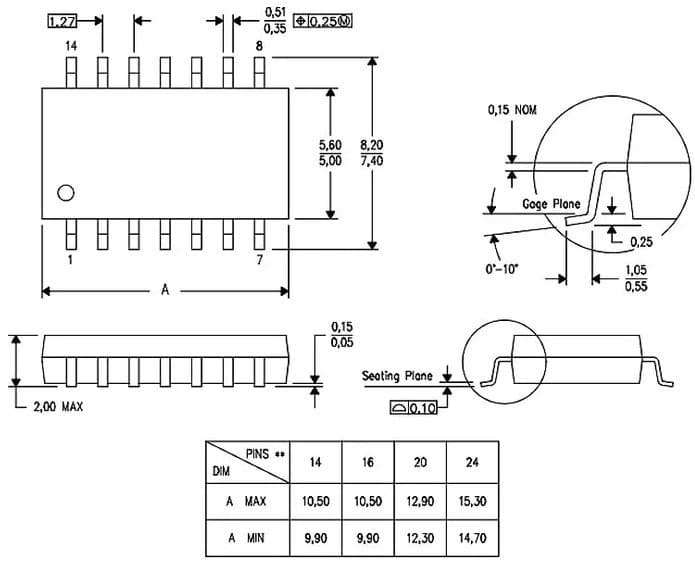

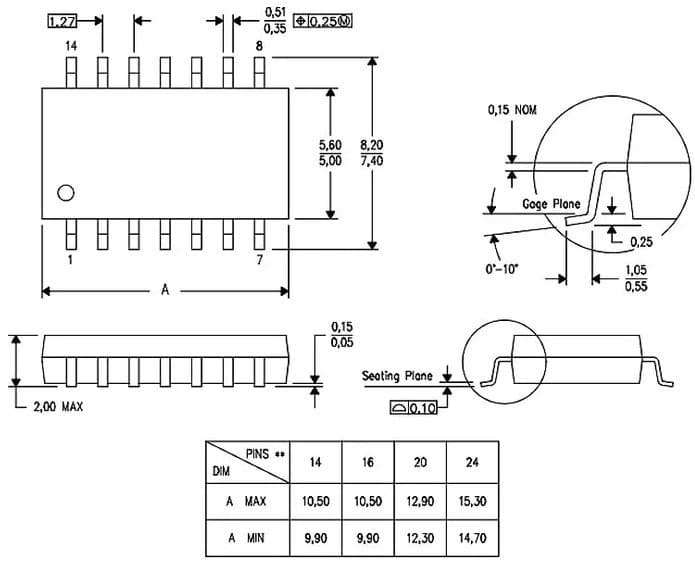

Sơ đồ 2D CD4068

Sơ đồ kích thước rất cần thiết khi thiết kế mạch PCB. Hình ảnh dưới đây là sơ đồ 2D của package DIP CD4068. Tải datasheet để biết thêm các package khác.

>>> Mời anh em xem thêm

Gối Đỡ Vòng Bi Cầu UCP (74)

Gối Đỡ Vòng Bi Cầu Mặt Bích Vuông UCF (65)

Gối Đỡ Vòng Bi Cầu UCPA (9)

Gối Đỡ Vòng Bi Cầu Mặt Bích Tròn UCFC (15)

Gối Đỡ Vòng Bi Cầu Mặt Bích Hình Thoi UCFL (20)

Gối Đỡ Vòng Bi Cầu Chữ T UCT (20)

Gối Đỡ Vòng Bi Đũa UCP (3)

Gối Đỡ Vòng Bi Đũa Mặt Bích Vuông UCF (1)

Gối Đỡ Vòng Bi Mắt Trâu (20)

Gối Đỡ Hai Nửa (31)

Măng Xông Vòng Bi (3)

Vòng Bi UC - UK (82)

Vỏ Gối Đỡ (1)

Vòng Đệm Khóa (22)

Phụ Kiện Gối Đỡ (54)

Con Lăn Bi Loại Ép Chặt (7)

Con Lăn Bi Loại Thân Lục Giác (8)

Con Lăn Bi Loại Thân Tròn (5)

Con Lăn Bi Loại Đế Mặt Bích (3)

Con Lăn Bi Loại Đinh Tán Đầu Tròn (4)

Con Lăn Bi Loại Vít Cấy (4)

Con Lăn Bi Loại Đẩy Bi Không Ren (3)

Ball Rollers Press (1)

Ball Plungers Roller (10)

Press Fit Plungers Roller (6)

Bộ Đầu Cos - Terminal Kits (3)

Đầu Cosse Chĩa Chữ Y (38)

Đầu Cosse Tròn (132)

Đầu Cosse Bít SC - TL (75)

Đầu Cosse Ghim (54)

Đầu Cosse Pin Đặc (19)

Đầu Cosse Pin Dẹp (22)

Đầu Cosse Pin Rỗng (77)

Đầu Cosse Nối Thẳng (31)

Đầu Cosse Chụp Nối Dây (8)

Đầu Cosse Vuông (8)

Mũ Chụp Đầu Cosse (127)

Giắc Cắm Điện Ô Tô (14)

Others of Vòng Bi

Others of Vòng Bi

![[TOP 07] Review Máy Nén Khí Fusheng Tốt Nhất (2023)](https://cms.mecsu.vn/uploads/media/2023/08/nen-chon-may-nen-khi-fusheng-nao-630x420.jpg)